Hindawi Publishing Corporation Journal of Nanotechnology Volume 2011, Article ID 823680, 4 pages doi:10.1155/2011/823680

# Research Article

# All-Printed Thin-Film Transistor Based on Purified Single-Walled Carbon Nanotubes with Linear Response

Guiru Gu,¹ Yunfeng Ling,¹ Runyu Liu,¹ Puminun Vasinajindakaw,¹ Xuejun Lu,¹ Carissa S. Jones,² Wu-Sheng Shih,² Vijaya Kayastha,² Nick L. Downing,² Xuliang Han,³ Harish Subbaraman,⁴ Dan Pham,⁵ Ray T. Chen,⁵ Maggie Yihong Chen,⁶ Urs Berger,² and Mike Renn²

Correspondence should be addressed to Xuejun Lu, xuejun lu@uml.edu

Received 29 April 2011; Revised 1 July 2011; Accepted 7 July 2011

Academic Editor: Yoke Khin Yap

Copyright © 2011 Guiru Gu et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

We report an all-printed thin-film transistor (TFT) on a polyimide substrate with linear transconductance response. The TFT is based on our purified single-walled carbon nanotube (SWCNT) solution that is primarily consists of semiconducting carbon nanotubes (CNTs) with low metal impurities. The all-printed TFT exhibits a high ON/OFF ratio of around 10³ and bias-independent transconductance over a certain gate bias range. Such bias-independent transconductance property is different from that of conventional metal-oxide-semiconductor field-effect transistors (MOSFETs) due to the special band structure and the one-dimensional (1D) quantum confined density of state (DOS) of CNTs. The bias-independent transconductance promises modulation linearity for analog electronics.

### 1. Introduction

Printable flexible electronics technology offers a costeffective way to achieve mass production of large-area flexible electronic circuits without using special lithography

equipment. It is expected to offer an enabling technology

for numerous applications, particularly those that require or

may benefit from the use of flexible polymeric substrates,

such as inflatable antennas, electronic papers, RF identification (RFID) tags, smart skins, and flat panel displays. Due

to its mechanical flexibility and high field effect mobility,

carbon nanotube (CNT) has shown great promises in printable flexible electronics [1–5]. High mobility and high-speed

CNT-based printable thin-film transistor (TFT) have been

demonstrated [6–10]. In addition to its mechanical flexibility

and high field effect mobility, CNT is also a promising material for transistors with bias-independent transconductance due to the special band structure and the one-dimensional (1D) quantum confined density of state (DOS) of CNTs [11–14]. The band structure and the 1D DOS of CNT allow the CNT-based TFTs to possess near-ballistic electron transportation and bias-independent transconductance [12, 13]. Such bias-independent transconductance is called inherent linearity [12] (referred it to as linear response or linear CNT-TFT, henceforth). The bias-independent transconductance is different from conventional metal-oxide-semiconductor field-effect transistors (MOSFETs) and is highly desired in many analog RF devices such as low noise amplifiers and power amplifiers [11–13]. However, most linear CNT-TFTs reported to date are based on CNTs grown by using the

<sup>&</sup>lt;sup>1</sup> Department of Electrical and Computer Engineering, University of Massachusetts Lowell, One University Avenue, Lowell, MA 01854, USA

<sup>&</sup>lt;sup>2</sup> Advanced Technologies R&D, Brewer Science, Inc., 2401 Brewer Drive, Rolla, MO 65401, USA

<sup>&</sup>lt;sup>3</sup> 11821 Sterling Panorama Ter, Austin, TX 78738, USA

<sup>&</sup>lt;sup>4</sup>Omega Optics, 10306 Sausalito Drive, Austin, TX 78759, USA

<sup>&</sup>lt;sup>5</sup> Microelectronics Center, University of Texas Austin, 10100 Burnet Road, Austin, TX 78758, USA

<sup>&</sup>lt;sup>6</sup> Electrical Engineering, Ingram School of Engineering, Texas State University, San Marcos, TX 78666, USA

<sup>&</sup>lt;sup>7</sup> Optomec, Inc., 3911 Singer Boulevard NE, Albuquerque, NM 87109, USA

chemical vapor deposition (CVD) grown method [12, 13] to obtain semiconducting CNTs with good alignment between the source (S) and drain (D) electrodes [13]. While high density aligned CNTs can achieve the highest performance [13], however, due to the high CVD-growth temperature of over 900°C, the CVD grown CNTs are not suitable for the development of printed flexible electronic devices [9]. Purified CNT solutions allow one to print CNT networks on flexible substrates with high field-effect electron mobility [9] and high-speed performance [10] for above-mentioned low-cost printed flexible electronics applications. In this paper, we evaluate the linear response of a CNT-TFT printed at room temperature using our purified single-walled carbon nanotube (SWCNT) solution consisting primarily of semiconducting carbon nanotubes (CNTs) with low metal impurities. The all-printed TFT shows a high ON/OFF ratio of around 10<sup>3</sup> and bias-independent transconductance over a certain gate bias range. Subthreshold swings of the allprinted TFT are also analyzed and agree well with the CVDgrown CNT-TFTs [12, 13]. The linear response shows that the printed CNT-TFT is promising for analog electronics that requires modulation linearity.

#### 2. Experiment

The all-printed SWCNT-TFT is in a top-gated configuration. It consists of source (S) and drain (D) electrodes, a carrier transport layer based on the purified SWCNT thin film, a gate dielectric layer, and a top gate electrode (G). The highly pure, additive-free, aqueous, SWCNT ink is prepared by Brewer Science Inc. The average tube diameter of the SWCNT is 0.8 nm. The length of the SWCNT varies from a few hundred nm to  $1 \mu m$ . The trace metal impurity concentration is measured to be <500 ppb. The width (W) of the source and drain electrodes is 500  $\mu$ m, and the separation between the source and drain electrodes, that is, channel length (L), is 50  $\mu$ m. All of these TFT elements were printed on a DuPont Kapton FPC polyimide film [15] by using an Optomec's Aerosol Jet printing system [16]. The source and drain electrodes were first printed on the Kapton FPC polyimide film using UTD Ag silver nanoink from UT-Dots. The active carrier transport layer was then printed, followed by the printing of the gate. Detailed printing process of the SWCNT-TFT is reported elsewhere [10].

#### 3. Results and Discussion

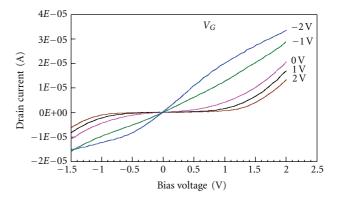

Figure 1 shows the source-drain I-V characteristics (ID versus VDS) of the SWCNT-TFT at different gate voltages (VG) from  $-2.0\,\mathrm{V}$  to  $+2.0\,\mathrm{V}$ . At the same source-drain voltage (VDS), the drain current (ID) decreases as the gate voltage increases from  $-2.0\,\mathrm{V}$  to  $2.0\,\mathrm{V}$ , suggesting that the SWCNT layer is a p-type carrier (hole) transportation channel [10]. At low source-drain voltages |VDS|  $< 1.0\,\mathrm{V}$ , the gate voltage of  $+2.0\,\mathrm{V}$  can effectively reduce the drain current.

At a gate bias of  $0\,\mathrm{V}$ , a turn-on voltage of  $1.0\,\mathrm{V}$  is observed, indicating Schottky barriers formed between the CNT and the source (S) and drain (D) electrodes. At the

FIGURE 1: Source-drain I-V characteristics (I<sub>D</sub> versus V<sub>DS</sub>) of the CNT-TFT at different gate voltages (V<sub>G</sub>). At the same source-drain voltage (V<sub>DS</sub>), the drain current (I<sub>D</sub>) decreases as the gate voltage increases from  $-2.0\,V$  to  $2.0\,V$ , suggesting that the SWCNT layer is a p-type carrier (hole) transportation channel.

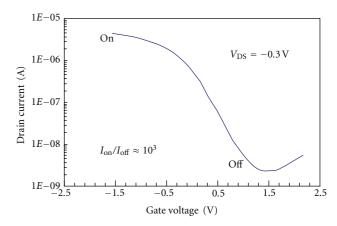

FIGURE 2: Drain current  $I_D$  versus  $V_G$  curves at the source-drain voltage  $V_{\rm DS}$  of -0.3 V. A high ON/OFF ratio of  $\sim 10^3$  is obtained.

gate biases of  $1.0\,\mathrm{V}$  and  $2.0\,\mathrm{V}$ , a larger turn-on voltages of  $1.3\,\mathrm{V}$  and  $1.4\,\mathrm{V}$  are measured, respectively. This reflects that the SWCNT band-bending can be tuned by the gate bias, which changes the Schottky barriers and leads to the turn-on voltage variations. At a gate bias of  $-1.0\,\mathrm{V}$ , a nearly linear I-V curve is obtained, indicating the transition from Schottky barrier to Ohmic contact at the SWCNT and the S and D electrode interfaces.

Figure 2 shows the drain current, the  $I_D$ , versus  $V_G$  curve at the source-drain voltages  $V_{\rm DS}$  of -0.3 V. As the gate voltage  $V_G$  increases from -2.0 V to +2.0 V, the drain current voltages  $I_D$  decreases from  $5.3 \times 10^{-6}$  (A) to  $5.4 \times 10^{-9}$  (A). If one defines ON and OFF states to be the maximum and minimum steady drain currents  $I_D$ , respectively, a high ON/OFF ratio of  $\sim 10^3$  is obtained with a low gate voltage tuning from -2.0 V to +2.0 V. Since metallic CNTs are conducting materials that are not affected by the gate field effect, the low drain current  $I_D$  at the OFF state and the effective gate control of the SWCNT channel indicate that the concentration of the metallic CNT is low in the SWCNT-TFT and the SWCNT is primarily semiconducting CNT.

Journal of Nanotechnology 3

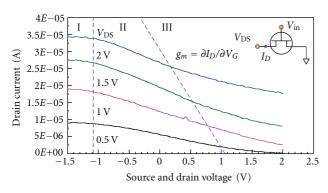

FIGURE 3: Drain current  $I_D$  versus  $V_G$  curves at different source-drain voltages  $V_{DS}$ . The inset shows the testing configuration. The  $I_D$  versus  $V_G$  curves can be divided into I, II, and III regions separated dashed lines.

Table 1: Transconductance at different  $V_{DS}$  in the linear region.

| Source and drain voltage $V_{\rm DS}$ | 0.5 V               | 1.0 V                | 1.5 V               | 2.0 V     |

|---------------------------------------|---------------------|----------------------|---------------------|-----------|

| Transconductance $g_m$                | $-3.5\mu\text{A/V}$ | $-5.7 \mu\text{A/V}$ | $-7.4\mu\text{A/V}$ | -7.5 μA/V |

Figure 3 shows the drain current  $I_D$  versus  $V_G$  curves at different source-drain voltages  $V_{\rm DS}$ . The inset in Figure 3 shows the testing configuration. The  $I_D$  versus  $V_G$  curves can be divided into three regions separated by dashed lines. The three regions are marked in Figure 3 as I, II, and III, respectively. The regions have different transconductances  $g_M = \partial I_D/\partial V_G$ . Region I is when  $V_G < -1.0\,\rm V$ , the drain current  $I_D$  varies little with the gate bias voltage  $V_G$  (referred to as the saturation region henceforth). The transconductances in this region are low ( $\sim -2\,\mu\rm A/V$ ) for all the different source-drain voltages  $V_{\rm DS}$  from 0.5 V to 2.0 V. Region II is between the two dashed lines. In this region, the  $I_D$  versus  $V_G$  curves are linear (referred to the linear region henceforth). The transconductances  $g_M$  at different  $V_{\rm DS}$  in the region are listed in Table 1.

In Table 1, it is shown that the transconductance varies little with  $V_{\rm DS}$  and it stays as a constant when  $V_{\rm DS} > 1.0 \, \rm V$ . For a conventional MOSFET, the drain current  $I_D$  is related to the  $V_{\rm DS}$  in the linear region by the following equation [17]:

$$I_D = \frac{W}{I} \mu_n C_{\text{ox}} \left( V_G - V_T - \frac{V_{\text{DS}}}{2} \right) V_{\text{DS}}, \tag{1}$$

where  $\mu_n$  is the mobility of an electron,  $C_{\rm ox}$  is the oxide capacitance per area, L is the channel length, and  $V_T$  is the threshold voltage. From (1), the transconductance of a conventional MOSFET  $g_m = \partial I_D/\partial V_G$  is proportional to  $V_{\rm DS}$ , whereas it is independent of  $V_{\rm DS}$  for the all-printed SWCNT-FET in Region II. The difference is attributed to the 1D quantum confined DOS of CNTs [12].

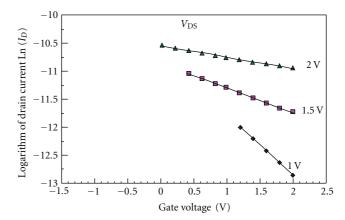

Region III is located to the right side of the second dashed line where the gate biases are positive. Figure 4 shows the logarithmic plots of the  $I_D$  versus  $V_G$  curves in this region. Linear dependence of natural logarithm of the drain current  $\ln(I_D)$  on the gate voltage  $V_G$  is obtained in this region,

FIGURE 4: Logarithmic plots of the  $I_D$  versus  $V_G$  curves in the region III of Figure 3. The dashed lines indicated linear dependence of natural logarithm of the drain current  $\ln(I_D)$  on the gate voltage  $V_G$ .

indicating exponential dependence of the drain current  $I_D$  on the gate voltage  $V_G$ . This is similar to a conventional MOSFET in the subthreshold region [17]. The subthreshold slopes are calculated to be 2.1 V/decade, 5.2 V/decade, and 10.3 V/decade at the drain voltages of 1.0 V, 1.5 V, and 2.0 V, respectively. The subthreshold I-V characteristics of an ideal CNT TFT can be expressed as [12]

$$I_D = \frac{4ekT}{h} \exp\left[\frac{e(V_G - V_T)}{kT}\right],\tag{2}$$

where e is the charge of an electron, h is the Planck's constant, k is the Boltzmann's constant, and  $V_T$  is the threshold voltage. Equation (2) shows that below threshold the drain current  $I_D$  has an exponential dependence on  $V_G - V_T$  at a rate of  $kT/e = 26 \,\mathrm{mV}$  at room temperature  $T = 300 \,\mathrm{K}$ . However, the printed SWCNT TFT shows a lower exponential dependence rate of 0.9 V, 2.2 V, and 4.5 V, at the drain voltages of 1.0 V, 1.5 V, and 2.0 V, respectively. The lower subthreshold slope was also reported [18]. This indicates that the gate bias has a less effective control of the drain current  $I_D$  than the ideal CNT TFT. This is possibly due to the electric field screening of the gate bias due to the movement of local charges (electron or ions) stored in the gate dielectric [19]. This electric field screening effect is subject to further investigation.

#### 4. Conclusion

In this paper, we demonstrated an all-printed flexible TFT based on the purified SWCNT solution. A high ON/OFF ratio of  $\sim\!10^3$  is obtained. The SWCNT-TFT also shows a linear transconductance region where the transconductance varies little with source and drain voltage bias  $V_{\rm DS}$ . Subthreshold swings of the all printed TFT are also analyzed and agree well with the CVD-grown CNT-TFTs [12, 13]. The preliminary demonstration of the linear TFT with high ON/OFF ratio bias-independent transconductance indicates that all-printed flexible TFT based on the purified SWCNT solution is promising for analog RF electronics applications.

## Acknowledgments

This research is supported by AFOSR, under Award FA9550-08-1-0070, and NSF STTR Phase II, under Award IIP0924536, and NASA SBIR Phase II, under contract no. NNX09CA37C.

#### References

- [1] K. Bradley, J.-C.P. Gabriel, and G. Gruner, "Flexible nanotube electronics," *Nano Letters*, vol. 3, no. 10, pp. 1353–1355, 2003.

- [2] E. S. Snow, J. P. Novak, P. M. Campbell, and D. Park, "Random networks of carbon nanotubes as an electronic material," *Applied Physics Letters*, vol. 82, no. 13, pp. 2145–2147, 2003.

- [3] E. Artukovic, M. Kaempgen, D. S. Hecht, S. Roth, and G. Gruner, "Transparent and flexible carbon nanotube transistors," *Nano Letters*, vol. 5, no. 4, pp. 757–760, 2005.

- [4] E. S. Snow, P. M. Campbell, M. G. Ancona, and J. P. Novak, "High-mobility carbon-nanotube thin-film transistors on a polymeric substrate," *Applied Physics Letters*, vol. 86, no. 3, Article ID 033105, pp. 1–3, 2005.

- [5] A. A. Pesetski, J. E. Baumgardner, S. V. Krishnaswamy et al., "A 500 MHz carbon nanotube transistor oscillator," *Applied Physics Letters*, vol. 93, no. 12, Article ID 123506, 2008.

- [6] S.-H. Hur, C. Kocabas, A. Gaur, O. O. Park, M. Shim, and J. A. Rogers, "Printed thin-film transistors and complementary logic gates that use polymer-coated single-walled carbon nanotube networks," *Journal of Applied Physics*, vol. 98, no. 11, Article ID 114302, pp. 1–6, 2005.

- [7] M. Ha, Y. Xia, A. Green et al., "Printed, sub-3V digital circuits on plastic from aqueous carbon nanotube inks," ACS Nano, vol. 4, no. 8, pp. 4388–4395, 2010.

- [8] E. Gracia-Espino, G. Sala, F. Pino et al., "Electrical transport and field-effect transistors using inkjet-printed SWCNT films having different functional side groups," *ACS Nano*, vol. 4, no. 6, pp. 3318–3324, 2010.

- [9] J. Vaillancourt, X. Lu, X. Han, and D. C. Janzen, "High-speed thin-film transistor on flexible substrate fabricated at room temperature," *Electronics Letters*, vol. 42, no. 23, pp. 1365– 1367, 2006.

- [10] J. Vaillancourt, H. Zhang, P. Vasinajindakaw et al., "All ink-jet-printed carbon nanotube thin-film transistor on a polyimide substrate with an ultrahigh operating frequency of over 5 GHz," *Applied Physics Letters*, vol. 93, no. 24, Article ID 243301, 3 pages, 2008.

- [11] H. Zhang, J. A. Payne, A. A. Pesetski et al., "High performance carbon nanotube RF electronics," in *Proceedings of the 66th IEEE Device Research Conference (DRC '08)*, pp. 13–14, Santa Barbara, Calif, USA, June 2008.

- [12] J. E. Baumgardner, A. A. Pesetski, J. M. Murduck, J. X. Przybysz, J. D. Adam, and H. Zhang, "Inherent linearity in carbon nanotube field-effect transistors," *Applied Physics Letters*, vol. 91, no. 5, Article ID 052107, 3 pages, 2007.

- [13] C. Rutherglen, D. Jain, and P. Burke, "Nanotube electronics for radio frequency applications," *Nature Nanotechnology*, vol. 4, no. 12, pp. 811–819, 2009.

- [14] J. W. Mintmire and C. T. White, "Universal density of states for carbon nanotubes," *Physical Review Letters*, vol. 81, no. 12, pp. 2506–2509, 1998.

- [15] Dupont Kapton product data sheet: (http://www2.dupont. com/Kapton/en\_US/assets/downloads/pdf/FPC\_datasheet.pdf).

- [16] Optomec product: (http://www.optomec.com/Additive-Manufacturing-Systems/Printed-Electronics-Lab-Systems).

- [17] S. M. Sze, *Physics of Semiconductor Devices*, John Wiley & Sons, New York, NY, USA, 3rd edition, 2007.

- [18] S. J. Wind, J. Appenzeller, R. Martel, V. Derycke, and P. Avouris, "Vertical scaling of carbon nanotube field-effect transistors using top gate electrodes," *Applied Physics Letters*, vol. 80, no. 20, pp. 3817–3819, 2002.

- [19] M. S. Fuhrer, B. M. Kim, T. Dürkop, and T. Brintlinger, "High-mobility nanotube transistor memory," *Nano Letters*, vol. 2, no. 7, pp. 755–759, 2002.